”时钟“ 的搜索结果

嵌入式学习(三)——时钟

标签: arm开发

时钟

标签: 源码下载 微信小程序

时钟源码

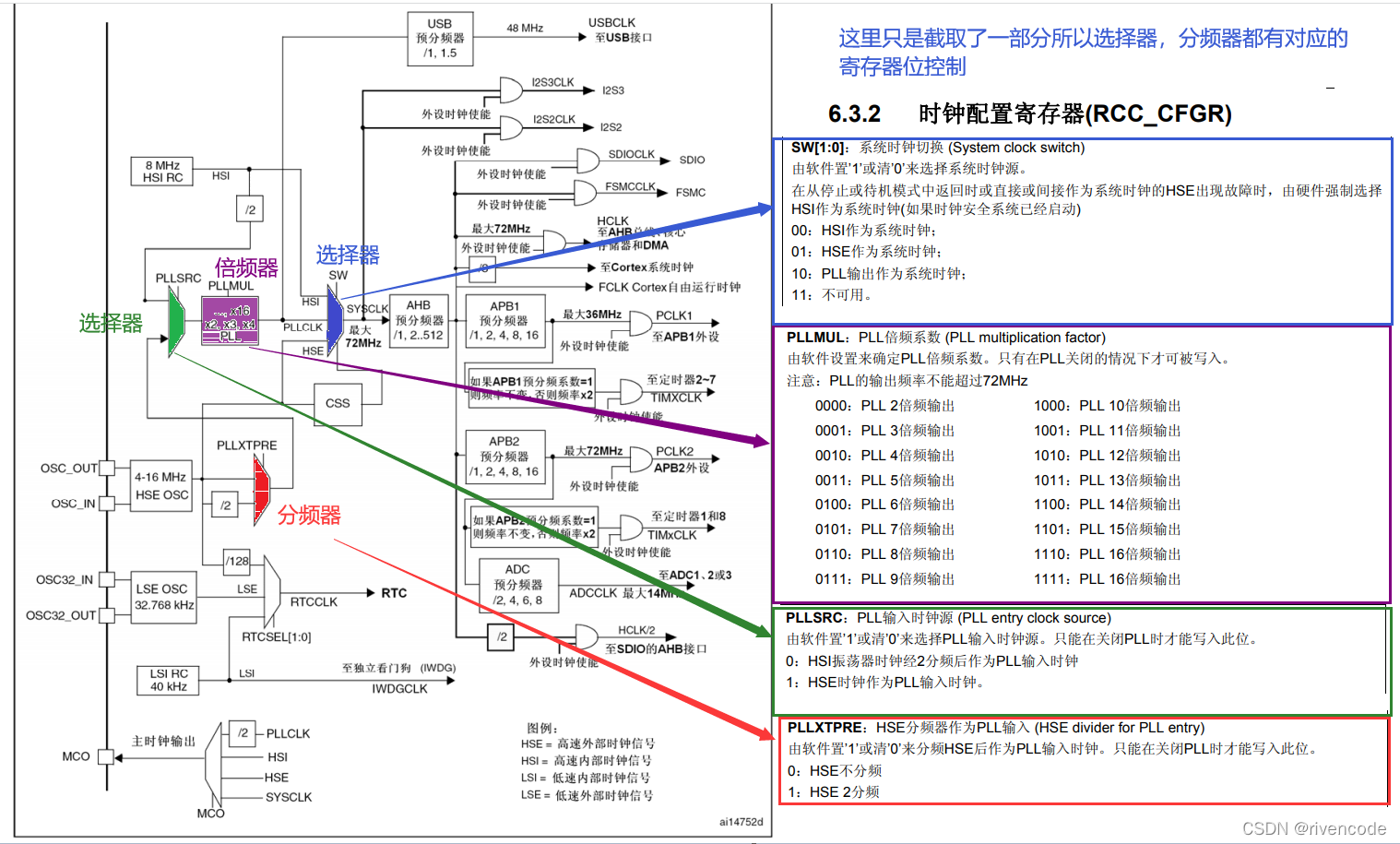

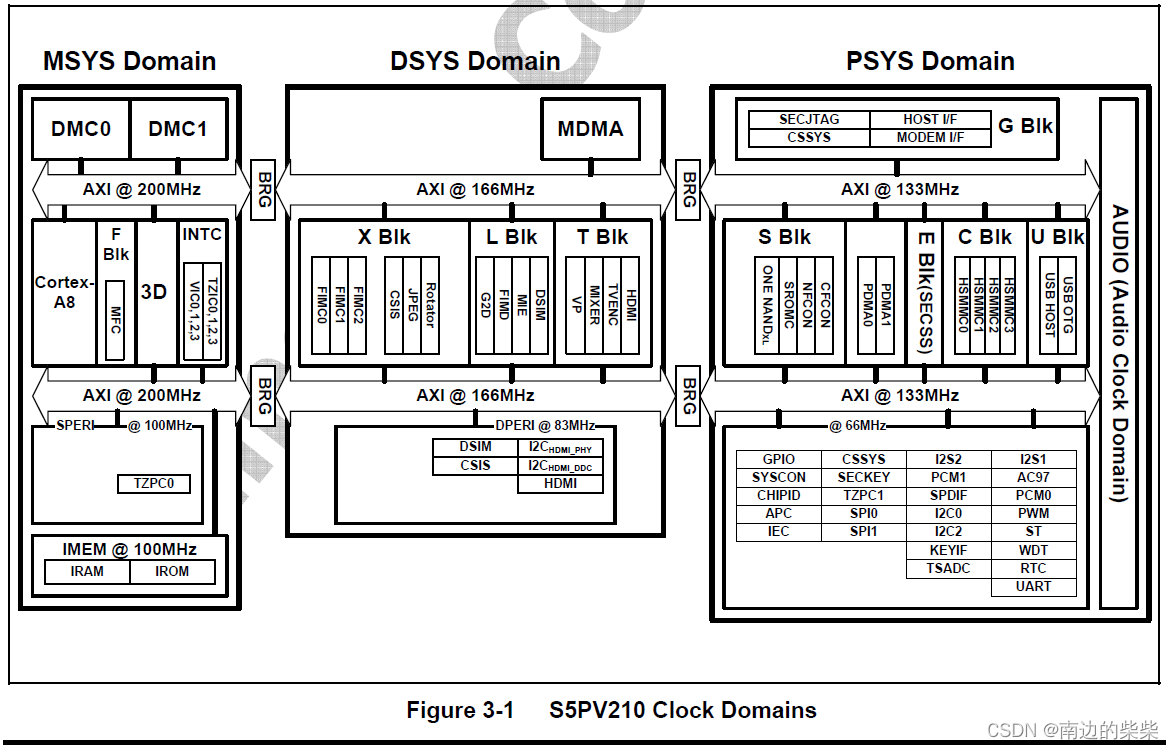

时钟是嵌入式系统的脉搏,处理器内核在时钟驱动下完成指令执行,状态变换等动作,外设部件在时钟的驱动下完成各种工作,例如:串口数据的发送、AD转换、定时器计数等。由系统时钟SYSCLK分频得到,一般不分频,等于...

金税盘时钟修复工具-(2月7日版本)TaxCloudSetup正式版2.0.0300.20210205.1053.exe

时钟功能 还有闹钟功能,温湿度功能,整点报时功能 你值得拥有

CDC:跨时钟域处理

标签: CDC

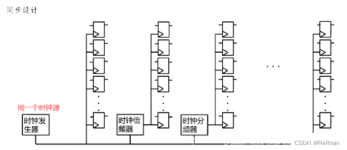

CDC(clock domain crossing)检查(跨时钟域的检查)是对电路设计中同步电路设计的检查。非同步时钟没有固定的相位关系,这样Setup/Hold不满足而产生了亚稳态是无法避免的。我们采用同步设计的方法保证亚稳态不会...

在FPGA和ASIC设计中,时钟信号的好坏很大程度上影响了整个系统的稳定性,本文主要介绍了数字设计中的非理想时钟的偏差来源与影响。

时钟树综合(CTS)

标签: 硬件工程

主时钟通常是FPGA器件外部的板级时钟(如晶振、数据传输的同步时钟等)或FPGA的高速收发器输出数据的同步恢复时钟信号等。

FPGA时钟资源,全局时钟,区域时钟,I/O时钟,CMT简介

(1)所有时钟的时钟来自同一个时钟源:比如下面的(分频电路) CLKA、CLKC、CLKD、CLKE都是由300M这个时钟源分频而来,因此这个系统属于同步电路系统。 (2)当不是来自同一个时钟源时,只要CLOCK的周期有倍数关系...

本文就PCIe Receiver内部恢复时钟与本地时钟之前的关系根据弹性缓冲的相关资料做一个浅显的学习整理,如有读者发现问题或错误,请慷慨指出,后期也会持续修正优化,谢谢! 对于PCIe总线的数据传输,我们知道其相...

STM32的时钟树介绍

推荐文章

- 什么是ABA问题及ABA问题的解决方法。-程序员宅基地

- muduo库的Singleton类剖析_muduo网络库中的sinleton类是干嘛的-程序员宅基地

- attach java_【JAVA新生】nio attach引发的问题-程序员宅基地

- 位掩码(bitmask)在windows 串口事件驱动中的应用_windows返回bitmask的函数-程序员宅基地

- 【STL】stack & queue & priority_queue {栈,队列,优先级队列的介绍及使用;仿函数/函数对象;容器适配器,双端队列deque}_容器link、队列、栈、优先队列、bitset的使用方法-程序员宅基地

- Java泛型——限制可用类型_java 泛型 限制类型-程序员宅基地

- 冲刺港股IPO,速腾聚创「承压」-程序员宅基地

- C++中istringstream、ostringstream、stringstream详细介绍和使用_c++ istringstream-程序员宅基地

- Java面试之JUC系列: 阻塞队列详细解析_java实现阻塞队列面试-程序员宅基地

- WebUploader 大文件上传解决方案(500M以上)_webuploader 大小限制-程序员宅基地